x86 - x86

| Designer | Intel , AMD |

|---|---|

| Biți | 16 biți , 32 biți și 64 biți |

| Introdus | 1978 (16 biți), 1985 (32 biți), 2003 (64 biți) |

| Proiecta | CISC |

| Tip | Înregistrare – memorie |

| Codificare | Variabilă (1 până la 15 octeți) |

| Ramificare | Codul condiției |

| Endianitate | Mic |

| Mărimea paginii |

8086 - i286 : Nici unul i386 , i486 : 4 KB pagini P5 Pentium : adăugat 4 MB pagini (Legacy PAE : 4 KB → 2 MB) x86-64 : adăugat 1 GB pagini |

| Extensii | x87 , IA-32 , x86-64 , MMX , 3D Acum! , SSE , MCA , ACPI , SSE2 , NX bit , SSE3 , SSSE3 , SSE4 , SSE4.2 , AES-NI , CLMUL , RDRAND , SHA , MPX , SME , SGX , XOP , F16C , ADX , BMI , FMA , AVX , AVX2 , AVX512 , VT-x , VT-d , AMD-V , AMD-Vi , TSX , ASF , TXT |

| Deschis | Parţial. Pentru unele caracteristici avansate, x86 poate necesita licență de la Intel; x86-64 poate necesita o licență suplimentară de la AMD. Procesorul 80486 este pe piață de mai bine de 30 de ani și, prin urmare, nu poate face obiectul revendicărilor de brevet. Prin urmare, subsetul pre-586 al arhitecturii x86 este complet deschis. |

| Registrele | |

| Scop general |

|

| Punctul de plutire | |

x86 este o familie de arhitecturi de seturi de instrucțiuni dezvoltate inițial de Intel pe baza microprocesorului Intel 8086 și a variantei sale 8088 . 8086 a fost introdus în 1978 ca o extensie completă pe 16 biți a microprocesorului Intel 8080 pe 8 biți , cu segmentarea memoriei ca soluție pentru adresarea mai multor memorii decât poate fi acoperită de o adresă simplă pe 16 biți. Termenul „x86” a apărut deoarece numele mai multor succesori ai procesorului Intel 8086 se termină în „86”, inclusiv procesorii 80186 , 80286 , 80386 și 80486 .

Multe adăugiri și extensii au fost adăugate la setul de instrucțiuni x86 de-a lungul anilor, aproape în mod consecvent, cu compatibilitate completă înapoi . Arhitectura a fost implementată în procesoare de la Intel, Cyrix , AMD , VIA Technologies și multe alte companii; există, de asemenea, implementări deschise, cum ar fi platforma Zet SoC (în prezent inactivă). Cu toate acestea, dintre acestea, numai Intel, AMD, VIA Technologies și DM&P Electronics dețin licențe de arhitectură x86 și, dintre acestea, doar primele două produc activ modele moderne pe 64 de biți.

Termenul nu este sinonim cu compatibilitatea cu computerul IBM , deoarece acest lucru implică o multitudine de alte componente hardware ; sistemele încorporate și computerele de uz general foloseau cipuri x86 înainte de începerea pieței compatibile cu PC , unele dintre ele înainte de debutul IBM PC (1981).

Începând cu 2021, majoritatea calculatoarelor personale , laptopurilor și consolelor de joc vândute se bazează pe arhitectura x86, în timp ce categoriile mobile, cum ar fi smartphone-urile sau tabletele, sunt dominate de ARM ; la vârf, x86 continuă să domine stațiile de lucru cu calcul intensiv și segmentele de cloud computing , în timp ce cel mai rapid supercomputer este bazat pe ARM, iar primele 4 nu mai sunt bazate pe x86.

Prezentare generală

În anii 1980 și începutul anilor 1990, când 8088 și 80286 erau încă în uz comun, termenul x86 reprezenta de obicei orice procesor compatibil 8086. Astăzi, însă, x86 implică, de obicei, o compatibilitate binară, de asemenea, cu setul de instrucțiuni pe 32 de biți al 80386. Acest lucru se datorează faptului că acest set de instrucțiuni a devenit un numitor comun cel mai mic pentru multe sisteme de operare moderne și probabil, de asemenea, pentru că termenul a devenit comun după introducerea 80386 în 1985.

La câțiva ani după introducerea modelelor 8086 și 8088, Intel a adăugat o oarecare complexitate schemei sale de denumire și terminologiei, deoarece „iAPX” al ambițiosului, dar nefericit procesor Intel iAPX 432 a fost încercat pe cea mai reușită familie de chips-uri 8086 ca un fel de prefix la nivel de sistem. Un sistem 8086 , incluzând coprocesoare precum 8087 și 8089 , și cipuri de sistem mai simple specifice Intel, a fost astfel descris ca un sistem iAPX 86 . Au existat, de asemenea, termeni iRMX (pentru sistemele de operare), iSBC (pentru computerele cu o singură placă) și iSBX (pentru plăcile multimodule bazate pe arhitectura 8086), toate împreună la rubrica Microsystem 80 . Cu toate acestea, această schemă de denumire a fost destul de temporară, durând câțiva ani la începutul anilor 1980.

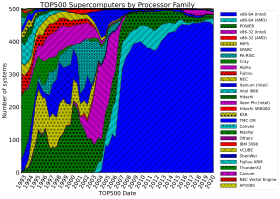

Deși 8086 a fost dezvoltat în principal pentru sisteme încorporate și computere mici multi-utilizator sau mono-utilizator, în mare parte ca răspuns la succesul Zilog Z80 , compatibil 8080 , linia x86 a crescut în curând în caracteristici și putere de procesare. Astăzi, x86 este omniprezent atât în calculatoarele personale staționare, cât și portabile, și este, de asemenea, utilizat în calculatoarele midrange , stații de lucru , servere și în majoritatea clusterelor noi de supercomputer din lista TOP500 . O cantitate mare de software , inclusiv o listă mare de sisteme de operare x86 utilizează hardware bazat pe x86.

Cu toate acestea, x86 modern este relativ neobișnuit în sistemele încorporate , iar aplicațiile mici de consum redus (folosind baterii mici) și piețele cu microprocesoare ieftine, cum ar fi aparatele electrocasnice și jucăriile, nu au o prezență x86 semnificativă. Simplu 8- și 16-biți arhitecturi bazate sunt comune aici, deși compatibile x86 VIA C7 , VIA Nano , AMD „s Geode , Athlon Neo și Intel Atom sunt exemple de 32- și 64-biți desene utilizate în unele relativ scăzute segmente de putere și low-cost.

Au existat mai multe încercări, inclusiv de către Intel, de a pune capăt dominanței pe piață a "inelegantului" arhitectură x86 proiectată direct de la primele microprocesoare simple pe 8 biți. Exemple în acest sens sunt iAPX 432 (un proiect numit inițial Intel 8800 ), Intel 960 , Intel 860 și arhitectura Intel / Hewlett-Packard Itanium . Cu toate acestea, rafinarea continuă a microarhitecturilor x86 , a circuitelor și a fabricării semiconductoarelor ar face dificilă înlocuirea x86 în multe segmente. Extensia AMD pe 64 de biți a x86 (la care Intel a răspuns în cele din urmă cu un design compatibil) și scalabilitatea cipurilor x86 sub formă de procesoare moderne multi-core, subliniază x86 ca exemplu al modului în care poate rezista rafinarea continuă a standardelor industriale stabilite. competiția de la arhitecturi complet noi.

Cronologie

Tabelul de mai jos prezintă modelele de procesoare și seriile de modele care implementează variații ale setului de instrucțiuni x86 , în ordine cronologică. Fiecare element rând se caracterizează prin proiecte de microarhitectură de procesor îmbunătățite semnificativ sau cu succes comercial .

| Generaţie | Introducere | Modele de CPU proeminente | Spațiu de adresă | Caracteristici notabile | |||

|---|---|---|---|---|---|---|---|

| Liniar | Virtual | Fizic | |||||

| x86 | Primul | 1978 | Intel 8086 , Intel 8088 (1979) | 16 biți | N / A | 20 de biți | ISA pe 16 biți , IBM PC (8088), IBM PC / XT (8088) |

| 1982 |

Intel 80186 , Intel 80188 NEC V20 / V30 (1983) |

8086-2 ISA, încorporat (80186/80188) | |||||

| Al 2-lea | Intel 80286 și clone | 30 de biți | 24 de biți | mod protejat , IBM PC / XT 286 , IBM PC / AT | |||

| 3 ( IA-32 ) | 1985 | Intel 80386 , AMD Am386 (1991) | Pe 32 de biți | 46 de biți | Pe 32 de biți | ISA pe 32 de biți , paginare, IBM PS / 2 | |

| Al 4-lea (pipelining, cache) | 1989 |

Intel 80486 Cyrix Cx486S , DLC (1992) AMD Am486 (1993), Am5x86 (1995) |

conducte , on-die x87 FPU (486DX), cache on-die | ||||

|

5 ( Superscalar ) |

1993 | Intel Pentium , Pentium MMX (1996) | Superscalar , bază de date pe 64 de biți , FPU mai rapid, MMX (Pentium MMX), APIC , SMP | ||||

| 1994 |

NexGen Nx586 AMD 5k86 / K5 (1996) |

Microarhitectură discretă (traducere µ-op) | |||||

| 1995 |

Cyrix Cx5x86 Cyrix 6x86 / MX (1997) / MII (1998) |

executie dinamica | |||||

|

6 ( PAE , traducere µ-op) |

1995 | Intel Pentium Pro | 36 de biți ( PAE ) | μ-op traducere, condiționale instrucțiuni de mutare, execuție dinamică , execuție speculativă , 3-way x86 superscalara, FPU superscalar, PAE , on-chip cache L2 | |||

| 1997 | Intel Pentium II , Pentium III (1999) Celeron (1998), Xeon (1998) |

on-package (Pentium II) sau on-die (Celeron) L2 Cache, SSE (Pentium III), SLOT 1 , Socket 370 sau SLOT 2 (Xeon) | |||||

| 1997 | AMD K6 / K6-2 (1998) / K6-III (1999) | Pe 32 de biți | 3DNow! , Sistem de cache pe 3 niveluri (K6-III) | ||||

| Platformă îmbunătățită | 1999 | AMD Athlon Athlon XP / MP (2001) Duron (2000) Sempron (2004) |

36 de biți | MMX +, 3DNow! +, Autobuz cu pompă dublă, slotul A sau soclul A. | |||

| 2000 | Transmeta Crusoe | Pe 32 de biți | Procesor cu platformă x86 alimentat CMS , core VLIW -128, controler de memorie on-die, logică bridge PCI on-die | ||||

| Intel Pentium 4 | 36 de biți | SSE2 , HTT (Northwood), NetBurst, autobuz cu patru pompe, Trace Cache, soclu 478 | |||||

| 2003 | Intel Pentium M Intel Core (2006) Pentium Dual-Core (2007) |

Fuziune µ-op , bit XD (Dothan) (Intel Core "Yonah") | |||||

| Transmeta Efficeon | CMS 6.0.4, VLIW -256, bit NX , HT | ||||||

| IA-64 | Tranziție pe 64 de biți 1999-2005 |

2001 | Intel Itanium (2001-2017) | 52 de biți | Arhitectură EPIC pe 64 de biți , pachet de instrucțiuni VLIW pe 128 de biți, hardware on-die IA-32 H / W care permite sisteme de operare x86 și aplicații x86 (primele generații), software IA-32 EL care permite aplicații x86 (Itanium 2), fișiere de registru Itanium sunt remapate la registrele x86 | ||

| x86-64 | 64-bit Extins din 2001 |

x86-64 este arhitectura extinsă pe 64 de biți a x86, modul său vechi păstrează întreaga și nealterată arhitectură x86. Arhitectura nativă a procesoarelor x86-64: rezidând în modul pe 64 de biți, lipsește modul de acces în segmentare, prezentând spațiu de adresă liniar arhitectural care permite 64 de biți; o arhitectură adaptată IA-32 care se află în modul de compatibilitate alături de modul pe 64 de biți este furnizată pentru a suporta majoritatea aplicațiilor x86 | |||||

| 2003 |

Athlon 64 / FX / X2 (2005), Opteron Sempron (2004) / X2 (2008) Turion 64 (2005) / X2 (2006) |

40 de biți | AMD64 ( cu excepția unor Sempron prezentate ca pur x86 procesoare), on-die controler de memorie, HyperTransport , on-die dual-core (X2), AMD-V (Athlon 64 Orleans), Socket 754 / 939 / la 940 sau AM2 | ||||

| 2004 |

Pentium 4 (Prescott) Celeron D , Pentium D (2005) |

36 de biți | EM64T (activat pe anumite modele de Pentium 4 și Celeron D), SSE3 , a doua generație. NetBurst pipelining, dual-core (on-die: Pentium D 8xx, on-chip: Pentium D 9xx), Intel VT (Pentium 4 6x2), soclu LGA 775 | ||||

| 2006 |

Intel Core 2 Pentium Dual-Core (2007) Celeron Dual-Core (2008) |

Intel 64 (<< == EM64T), SSSE3 (65 nm), execuție dinamică largă, fuziune µ-op, fuziune macro-op în mod pe 16 biți și 32 biți, quad-core on-chip (Core 2 Quad) , Cache partajat inteligent L2 (Intel Core 2 „Merom”) | |||||

| 2007 |

AMD Phenom / II (2008) Athlon II (2009) Turion II (2009) |

48 de biți | Monolitic quad-core (X4) / triple-core (X3), SSE4a , Rapid Virtualization Indexing (RVI), HyperTransport 3, AM2 + sau AM3 | ||||

| 2008 | Intel Core 2 (45 nm) | 40 de biți | SSE4.1 | ||||

| Intel Atom | netbook sau procesor de dispozitiv inteligent de consum redus, nucleu P54C reutilizat | ||||||

| Intel Core i7 Core i5 (2009) Core i3 (2010) |

QuickPath, on-chip GMCH ( Clarkdale ), SSE4.2 , Extended Page Tables (EPT) pentru virtualizare, fuziune macro-op în mod pe 64 de biți, (Intel Xeon "Bloomfield" cu microarhitectură Nehalem) | ||||||

| VIA Nano | criptare bazată pe hardware ; managementul adaptiv al puterii | ||||||

| 2010 | AMD FX | 48 de biți | octa-core, CMT (Clustered Multi-Thread), FMA, OpenCL, AM3 + | ||||

| 2011 | Seriile AMD APU A și E ( Llano ) | 40 de biți | GPGPU on-die, PCI Express 2.0, Socket FM1 | ||||

| AMD APU Seria C, E și Z ( Bobcat ) | 36 de biți | APU pentru dispozitiv inteligent de putere redusă | |||||

|

Intel Core i3 , Core i5 și Core i7 ( Sandy Bridge / Ivy Bridge ) |

Conexiune inel intern, cache µ-op decodat, soclu LGA 1155 | ||||||

| 2012 | AMD APU A Series ( Buldozer, Trinity și mai târziu) | 48 de biți | AVX , APU bazat pe buldozer, Socket FM2 sau Socket FM2 + | ||||

| Intel Xeon Phi (Knights Corner) | PCI-E add-on card de coprocesor pentru sistem bazat pe XEON, Manycore Chip, în ordinul P54C , foarte larg VPU (512-bit SSE), instrucțiuni de LRBni (8 x 64 biți) | ||||||

| 2013 | AMD Jaguar (Athlon, Sempron) |

SoC , consolă de jocuri și procesor de dispozitiv inteligent de mică putere | |||||

| Intel Silvermont (Atom, Celeron, Pentium) |

36 de biți | SoC , procesor de dispozitiv inteligent cu putere redusă / ultra-mică | |||||

| Intel Core i3 , Core i5 și Core i7 ( Haswell / Broadwell ) | 39 de biți | AVX2 , FMA3 , TSX , Bmi1 și BMI2 instrucțiuni, LGA 1150 soclu | |||||

| 2015 | Intel Broadwell-U ( Intel Core i3 , Core i5 , Core i7 , Core M , Pentium , Celeron ) |

SoC, on-chip Broadwell-U PCH-LP (modul multi-chip) | |||||

| 2015-2020 | Intel Skylake / Kaby Lake / Cannon Lake / Coffee Lake / Rocket Lake (Intel Pentium / Celeron Gold, Core i3 , Core i5 , Core i7 , Core i9 ) |

46 de biți | AVX-512 (limitat la Cannon Lake-U și variante de stație de lucru / server Skylake) | ||||

| 2016 | Intel Xeon Phi (Knights Landing) | 48 de biți | Procesor Manycore și coprocesor pentru sistemele Xeon, nucleu bazat pe Airmont (Atom) | ||||

| 2016 | AMD Bristol Ridge (AMD (Pro) A6 / A8 / A10 / A12) |

FCH integrat pe matriță, SoC, soclu AM4 | |||||

| 2017 | Seria AMD Ryzen / Seria AMD Epyc | Implementarea de către AMD a matrițelor multiple SMT, on-chip | |||||

| 2017 | Zhaoxin WuDaoKou (KX-5000, KH-20000) | Prima arhitectură x86-64 complet nouă a lui Zhaoxin | |||||

| 2018-2021 | Intel Sunny Cove (Ice Lake-U și Y), Cypress Cove (Rocket Lake) | 57 de biți | Prima implementare Intel a AVX-512 pentru segmentul consumatorilor. Adăugarea instrucțiunilor de rețea neuronală vectorială (VNNI) | ||||

| 2020 | Intel Willow Cove (Tiger Lake-Y / U / H) | Arhitectură de interconectare cu două inele, accelerator neuronal Gaussian (GNA2) actualizat, noi instrucțiuni de intersecție vectorială AVX-512, adăugarea tehnologiei Control-Flow Enforcement (CET) | |||||

| Eră | Eliberare | Modele CPU | Spațiu de adrese fizice | Functii noi | |||

Istorie

Alți producători

În diverse momente, companii precum IBM , VIA , NEC , AMD , TI , STM , Fujitsu , OKI , Siemens , Cyrix , Intersil , C&T , NexGen , UMC și DM&P au început să proiecteze sau să fabrice procesoare x86 (CPU) destinate personalului calculatoare și sisteme încorporate. Astfel de implementări x86 sunt rareori copii simple, dar adesea utilizează diferite microarhitecturi interne și soluții diferite la nivel electronic și fizic. În mod firesc, microprocesoarele compatibile timpurii erau pe 16 biți, în timp ce designurile pe 32 de biți au fost dezvoltate mult mai târziu. Pentru piața computerelor personale , cantități reale au început să apară în jurul anului 1990, cu procesoare compatibile i386 și i486 , denumite adesea similar cu cipurile originale Intel. Alte companii, care au proiectat sau fabricat procesoare x86 sau x87 , includ ITT Corporation , National Semiconductor , ULSI System Technology și Weitek .

În urma pe deplin pipeline i486 , Intel a introdus Pentium numele de brand (care, spre deosebire de numere, ar putea fi marcă înregistrată ) pentru noul set de superscalare modele x86. Cu schema de denumire x86 acum legală, alți furnizori de x86 au trebuit să aleagă nume diferite pentru produsele lor compatibile cu x86 și inițial unii au ales să continue cu variații ale schemei de numerotare: IBM a colaborat cu Cyrix pentru a produce modelul 5x86 și apoi foarte eficient Liniile 6x86 (M1) și 6x86 MX ( MII ) ale proiectelor Cyrix, care au fost primele microprocesoare x86 care implementează redenumirea registrelor pentru a permite executarea speculativă . Între timp, AMD a proiectat și fabricat 5k86 ( K5 ) avansat, dar întârziat , care, pe plan intern , se bazează îndeaproape pe designul anterior RISC 29K al AMD ; asemănător cu NexGen 's Nx586 , a folosit o strategie astfel încât etapele de conducte dedicate să decodifice instrucțiunile x86 în micro-operațiuni uniforme și ușor de manevrat , metodă care a rămas la baza majorității proiectelor x86 până în prezent.

Unele versiuni timpurii ale acestor microprocesoare au avut probleme de disipare a căldurii. 6x86 a fost, de asemenea, afectat de câteva probleme minore de compatibilitate, Nx586 nu avea o unitate cu virgulă mobilă (FPU) și (atunci crucială) compatibilitatea pin, în timp ce K5 avea performanțe oarecum dezamăgitoare când a fost (eventual) introdus. Necunoașterea de către clienți a alternativelor la seria Pentium a contribuit și mai mult la faptul că aceste modele au fost relativ nereușite, în ciuda faptului că K5 avea o compatibilitate Pentium foarte bună, iar modelul 6x86 era semnificativ mai rapid decât codul Pentium on integer. Mai târziu, AMD a reușit să devină un concurent serios cu setul de procesoare K6 , care a cedat locul succesului Athlon și Opteron . Au existat și alți concurenți, cum ar fi Centaur Technology (fost IDT ), Rise Technology și Transmeta . Procesoarele eficiente din punct de vedere energetic C3 și C7 ale VIA Technologies , care au fost proiectate de compania Centaur , au fost vândute de mulți ani. Cel mai nou design al Centaurului, VIA Nano , este primul lor procesor cu execuție superscalară și speculativă . A fost introdus cam în același timp cu primul procesor „în ordine” Intel de la P5 Pentium , Intel Atom .

Extensii ale dimensiunii cuvântului

Arhitectura set de instrucțiuni de două ori a fost extins la o mai mare cuvânt dimensiune. În 1985, Intel a lansat 80386 pe 32 de biți (mai târziu cunoscut sub numele de i386), care a înlocuit treptat cipurile anterioare de 16 biți din computere (deși de obicei nu sunt în sistemele încorporate ) în anii următori; acest model extins de programare a fost denumit inițial arhitectura i386 (la fel ca prima sa implementare), dar mai târziu Intel a numit-o IA-32 când a introdus arhitectura IA (fără legătură) IA-64 .

În 1999-2003, AMD a extins această arhitectură pe 32 de biți la 64 de biți și a denumit-o x86-64 în documentele anterioare și mai târziu AMD64 . Intel a adoptat în curând extensiile arhitecturale ale AMD sub numele IA-32e, folosind ulterior numele EM64T și folosind în cele din urmă Intel 64. Microsoft și Sun Microsystems / Oracle folosesc și termenul „x64”, în timp ce multe distribuții Linux și BSD - urile folosesc și „amd64 " termen. Microsoft Windows, de exemplu, desemnează versiunile sale pe 32 de biți ca „x86” și versiunile pe 64 de biți ca „x64”, în timp ce fișierele de instalare ale versiunilor Windows pe 64 de biți trebuie să fie plasate într-un director numit „AMD64”.

Proprietățile de bază ale arhitecturii

Arhitectura x86 are o lungime variabilă a instrucțiunilor, în primul rând proiectarea „ CISC ”, cu accent pe compatibilitatea inversă . Setul de instrucțiuni nu este totuși tipic CISC, ci practic o versiune extinsă a arhitecturilor simple pe 8 biți 8008 și 8080 . Adresarea de octeți este activată, iar cuvintele sunt stocate în memorie cu ordinea de octeți puțin endiană . Accesul la memorie la adrese nealiniate este permis pentru aproape toate instrucțiunile. Cea mai mare dimensiune nativă pentru aritmetica numerică și adresele de memorie (sau decalaje ) este de 16, 32 sau 64 de biți, în funcție de generarea arhitecturii (procesoarele mai noi includ suport direct și pentru numere întregi mai mici). Mai multe valori scalare pot fi gestionate simultan prin unitatea SIMD prezentă în generațiile ulterioare, așa cum este descris mai jos. Compensările de adresare imediată și datele imediate pot fi exprimate ca cantități de 8 biți pentru cazurile sau contextele frecvente în care este suficient un interval de -128..127. Instrucțiunile tipice au, prin urmare, o lungime de 2 sau 3 octeți (deși unele sunt mult mai lungi, iar altele sunt cu un singur octet).

Pentru a conserva în continuare spațiul de codare, majoritatea registrelor sunt exprimate în coduri opționale folosind trei sau patru biți, acesta din urmă printr-un prefix opcode în modul pe 64 de biți, în timp ce cel mult un operand la o instrucțiune poate fi o locație de memorie. Totuși, acest operand de memorie poate fi, de asemenea, destinația (sau o sursă și destinație combinate ), în timp ce celălalt operand, sursa , poate fi fie registru, fie imediat . Printre alți factori, acest lucru contribuie la o dimensiune a codului care rivalizează cu mașinile de opt biți și permite utilizarea eficientă a memoriei cache de instrucțiuni. Numărul relativ mic de registre generale (moștenite și de la strămoșii săi de 8 biți) a făcut din adresarea relativă a registrului (folosind mici compensări imediate) o metodă importantă de accesare a operanzilor, în special pe stivă. Prin urmare, s-a investit mult în realizarea unor astfel de accesări la fel de rapide ca accesurile la registru - adică, un flux de instrucțiuni cu un ciclu, în majoritatea circumstanțelor în care datele accesate sunt disponibile în memoria cache de nivel superior.

Virgulă mobilă și SIMD

Un procesor dedicat în virgulă mobilă cu registre interne pe 80 de biți, 8087 , a fost dezvoltat pentru 8086 original . Acest microprocesor s-a dezvoltat ulterior în 80387 extins , iar procesatoarele ulterioare au încorporat o versiune compatibilă înapoi a acestei funcționalități pe același microprocesor ca și procesorul principal. În plus, proiectele moderne x86 conțin și o unitate SIMD (a se vedea mai jos SSE ) în care instrucțiunile pot funcționa în paralel pe (unul sau două) cuvinte pe 128 de biți, fiecare conținând două sau patru numere în virgulă mobilă (fiecare 64 sau 32) biți lățime respectiv), sau alternativ, 2, 4, 8 sau 16 numere întregi (fiecare 64, 32, 16 sau respectiv 8 biți lățime).

Prezența unor registre SIMD largi înseamnă că procesoarele x86 existente pot încărca sau stoca până la 128 de biți de date de memorie într-o singură instrucțiune și, de asemenea, pot efectua operațiuni pe biți (deși nu aritmetice întregi) pe cantități complete de 128 de biți în paralel. Procesoarele Intel Sandy Bridge au adăugat instrucțiunile Advanced Vector Extensions (AVX), extinzând registrele SIMD la 256 de biți. Instrucțiunile Intel Initial Many Core implementate de procesoarele Knights Corner Xeon Phi și instrucțiunile AVX-512 implementate de procesoarele Knights Landing Xeon Phi și de procesoarele Skylake-X utilizează registre SIMD de 512 biți.

Implementări actuale

În timpul execuției , procesoarele x86 actuale folosesc câțiva pași suplimentari de decodare pentru a împărți majoritatea instrucțiunilor în bucăți mai mici numite micro-operațiuni. Acestea sunt apoi predate unei unități de control care le memorează și le programează în conformitate cu semantica x86, astfel încât să poată fi executate, parțial în paralel, de una dintre mai multe unități de execuție (mai mult sau mai puțin specializate) . Aceste modele moderne x86 sunt astfel canalizate , suprascalare și, de asemenea, capabile să nu funcționeze și să execute speculativ (prin predicția ramurilor , redenumirea registrului și predicția dependenței de memorie ), ceea ce înseamnă că pot executa instrucțiuni multiple (parțiale sau complete) x86 simultan și nu neapărat în aceeași ordine ca în fluxul de instrucțiuni. Unele procesoare Intel ( Xeon Foster MP , unele Pentium 4 și unele procesoare Nehalem și mai târziu Intel Core ) și procesoare AMD (începând de la Zen ) sunt, de asemenea, capabile să multiplice simultan cu două fire pentru fiecare nucleu ( Xeon Phi are patru fire pentru fiecare nucleu). Unele procesoare Intel acceptă memorie tranzacțională ( TSX ).

Când a fost introdusă, la mijlocul anilor 1990, această metodă a fost uneori denumită „nucleu RISC” sau „traducere RISC”, parțial din motive de marketing, dar și pentru că aceste micro-operațiuni împărtășesc unele proprietăți cu anumite tipuri de instrucțiuni RISC. Cu toate acestea, microcodul tradițional (utilizat din anii 1950) împărtășește, de asemenea, în mod inerent multe dintre aceleași proprietăți; noua metodă diferă în principal prin faptul că translația în micro-operații are loc acum asincron. Necesitatea sincronizării unităților de execuție cu pașii de decodare deschide posibilități pentru o analiză mai mare a fluxului de cod (tamponat) și, prin urmare, permite detectarea operațiunilor care pot fi efectuate în paralel, alimentând simultan mai mult de o unitate de execuție.

Ultimele procesoare fac, de asemenea, opusul atunci când este cazul; acestea combină anumite secvențe x86 (cum ar fi o comparație urmată de un salt condițional) într-un micro-op mai complex care se potrivește mai bine modelului de execuție și, astfel, poate fi executat mai rapid sau cu mai puține resurse de mașină implicate.

O altă modalitate de a încerca să îmbunătățiți performanța este de a memora în cache micro-operațiunile decodate, astfel încât procesorul să poată accesa direct micro-operațiile decodate dintr-un cache special, în loc să le decodeze din nou. Intel a urmat această abordare cu funcția Execution Trace Cache în microarhitectura NetBurst (pentru procesoarele Pentium 4) și mai târziu în Decoded Stream Buffer (pentru procesoarele marca Core de la Sandy Bridge).

Transmeta a folosit o metodă complet diferită în procesatoarele lor compatibile cu Crusoe x86. Au folosit traducerea just-in-time pentru a converti instrucțiunile x86 în setul de instrucțiuni VLIW nativ al procesorului . Transmeta a susținut că abordarea lor permite proiecte mai eficiente din punct de vedere energetic, deoarece CPU poate renunța la etapa complicată de decodare a implementărilor x86 mai tradiționale.

Segmentare

Minicomputerele de la sfârșitul anilor 1970 se confruntau cu limita de 16 biți de 64 KB , deoarece memoria devenise mai ieftină. Unele minicomputere, cum ar fi PDP-11, au folosit scheme complexe de comutare bancară sau, în cazul VAX- ului Digital , au reproiectat procesoare mult mai scumpe, care ar putea gestiona direct adresarea și datele pe 32 de biți. 8086 original, dezvoltat din microprocesorul simplu 8080 și care viza în primul rând computere foarte mici și ieftine și alte dispozitive specializate, a adoptat în schimb registre simple de segmente care au mărit lățimea adresei de memorie cu doar 4 biți. Înmulțind o adresă de 64 KB cu 16, adresa de 20 de biți ar putea aborda un total de un megabyte (1.048.576 octeți), ceea ce reprezenta o cantitate destul de mare pentru un computer mic în acel moment. Conceptul de registre de segmente nu a fost nou pentru multe mainframe-uri care au folosit registre de segmente pentru a trece rapid la diferite sarcini. În practică, pe x86 a fost (este) o implementare mult criticată, care a complicat mult multe sarcini comune de programare și compilatoare. Cu toate acestea, arhitectura a permis în curând adresarea liniară pe 32 de biți (începând cu 80386 la sfârșitul anului 1985), dar actorii majori (cum ar fi Microsoft ) au durat câțiva ani pentru a-și converti sistemele pe 16 biți. 80386 (și 80486) a fost, prin urmare, utilizat în mare măsură ca 8086 rapid (dar bazat pe 16 biți) timp de mulți ani.

Datele și codul ar putea fi gestionate în segmente „aproape” de 16 biți în 64 de porțiuni din spațiul total de adrese de 1 MB sau un compilator ar putea funcționa într-un mod „îndepărtat” folosind segment:offsetperechi de 32 de biți ajungând (doar) la 1 MB. Deși acest lucru s-ar dovedi a fi destul de limitativ la mijlocul anilor 1980, acesta funcționa pentru piața emergentă de PC-uri și a făcut foarte simplă traducerea software-ului de la vechile 8008 , 8080 , 8085 și Z80 la procesorul mai nou. În cursul anului 1985, modelul de adresare pe segment de 16 biți a fost efectiv luat în considerare prin introducerea registrelor de offset pe 32 de biți, în designul 386 .

În modul real , segmentarea se realizează prin deplasarea adresei de segment lăsate cu 4 biți și adăugarea unui offset pentru a primi o adresă finală de 20 de biți. De exemplu, dacă DS este A000h și SI este 5677h, DS: SI va indica adresa absolută DS × 10h + SI = A5677h. Astfel, spațiul total de adrese în modul real este de 2 20 octeți, sau 1 MB , o cifră destul de impresionantă pentru 1978. Toate adresele de memorie constau atât dintr-un segment, cât și din offset; fiecare tip de acces (cod, date sau stivă) are asociat un registru de segmente implicit (pentru date registrul este de obicei DS, pentru cod este CS, iar pentru stivă este SS). Pentru accesarea datelor, registrul de segmente poate fi specificat în mod explicit (folosind un prefix de suprascriere a segmentului) pentru a utiliza oricare dintre cele patru registre de segmente.

În această schemă, două perechi de segmente / offset diferite pot indica o singură locație absolută. Astfel, dacă DS este A111h și SI este 4567h, DS: SI va indica același A5677h ca mai sus. Această schemă face imposibilă utilizarea a mai mult de patru segmente simultan. CS și SS sunt vitale pentru funcționarea corectă a programului, astfel încât numai DS și ES pot fi utilizate pentru a indica segmentele de date din afara programului (sau, mai precis, în afara segmentului de executare curent al programului) sau stivei.

În modul protejat , introdus în 80286, un registru de segmente nu mai conține adresa fizică a începutului unui segment, ci conține un „selector” care indică o structură la nivel de sistem numită descriptor de segment . Un descriptor de segment conține adresa fizică de la începutul segmentului, lungimea segmentului și permisiunile de acces la acel segment. Decalajul este verificat în funcție de lungimea segmentului, cu decalaje care se referă la locațiile din afara segmentului provocând o excepție. Compensările care se referă la locațiile din interiorul segmentului sunt combinate cu adresa fizică de la începutul segmentului pentru a obține adresa fizică corespunzătoare acelei compensări.

Natura segmentată poate face dificilă programarea și proiectarea compilatorului, deoarece utilizarea indicatoarelor apropiate și îndepărtate afectează performanța.

Moduri de adresare

Modurile de adresare pentru modurile procesorului pe 16 biți pot fi rezumate prin formula:

Modurile de adresare pentru modurile de procesor x86 pe 32 de biți pot fi rezumate prin formula:

Modurile de adresare pentru modul procesor pe 64 de biți pot fi rezumate prin formula:

Adresarea relativă a instrucțiunilor în cod pe 64 de biți (deplasare RIP +, unde RIP este registrul indicatorului de instrucțiuni ) simplifică implementarea codului independent de poziție (așa cum este utilizat în bibliotecile partajate în unele sisteme de operare).

8086 avea 64 KB de opt biți (sau alternativ32 K-cuvânt de 16 biți ) spațiu I / O și a64 KB (un segment) stivă în memorie acceptată de hardware-ul computerului . Doar cuvintele (doi octeți) pot fi împinse în stivă. Stiva crește către adrese mai mici numeric, cu SS: SP îndreptându-se către cel mai recent element împins. Există 256 de întreruperi , care pot fi invocate atât de hardware, cât și de software. Întreruperile pot fi în cascadă, utilizând stiva pentru a stoca adresa de returnare .

registrele x86

16 biți

Originalele Intel 8086 și 8088 au paisprezece registre pe 16 biți . Patru dintre ele (AX, BX, CX, DX) sunt registre de uz general (GPR), deși fiecare poate avea un scop suplimentar; de exemplu, numai CX poate fi folosit ca contor cu instrucțiunea buclă . Fiecare poate fi accesat ca doi octeți separați (astfel octetul mare al BX poate fi accesat ca BH și octetul mic ca BL). Două registre de pointer au roluri speciale: SP (indicatorul stivei) indică „partea de sus” a stivei , iar BP (pointerul de bază) este adesea folosit pentru a indica un alt loc din stivă, de obicei deasupra variabilelor locale (vezi indicatorul cadrului) ). Registrele SI, DI, BX și BP sunt registre de adrese și pot fi folosite și pentru indexarea matricei.

Patru registre de segmente (CS, DS, SS și ES) sunt utilizate pentru a forma o adresă de memorie. Registrul FLAGS conține stegulețe, cum ar fi steagul de transport , steagul de deversare și steagul zero . În cele din urmă, indicatorul de instrucțiuni (IP) indică următoarea instrucțiune care va fi preluată din memorie și apoi executată; acest registru nu poate fi accesat direct (citit sau scris) de către un program.

Intel 80186 și 80188 sunt în esență un upgrade 8086 sau 8088 CPU, respectiv, cu periferice on-chip adăugată, și au aceleași registre CPU ca 8086 și 8088 (în plus față de registrele de interfață pentru periferice).

8086, 8088, 80186 și 80188 pot utiliza un coprocesor opțional în virgulă mobilă, 8087 . 8087 apare programatorului ca parte a procesorului și adaugă opt registre pe 80 de biți, st (0) la st (7), fiecare dintre acestea putând păstra date numerice într-unul din cele șapte formate: 32-, 64- sau Vârg plutitor pe 80 de biți, număr întreg de 16, 32 sau 64 de biți (binar) și număr întreg zecimal de 80 de biți. De asemenea, are propriul registru de stare pe 16 biți accesibil prin instrucțiunea fntsw și este obișnuit să folosiți pur și simplu unii dintre biții săi pentru ramificare, copiindu-l în FLAG-urile normale.

În Intel 80286 , pentru a accepta modul protejat , trei registre speciale conțin adrese de tabel descriptor (GDTR, LDTR , IDTR ) și un al patrulea registru de sarcini (TR) este utilizat pentru comutarea sarcinilor. 80287 este virgula mobila coprocesorul pentru 80286 și are aceleași registre ca și 8087 , cu aceleași formate de date.

Pe 32 de biți

Odată cu apariția procesorului 80386 pe 32 de biți , registrele de uz general de 16 biți, registrele de bază, registrele index, indicatorul de instrucțiuni și registrul FLAGS , dar nu și registrele de segmente, au fost extinse la 32 de biți. Nomenclatura a reprezentat acest lucru prin prefixarea unui „ E ” (pentru „extins”) la numele registrelor în limbajul de asamblare x86 . Astfel, registrul AX corespunde celor mai mici 16 biți ai noului registru EAX pe 32 de biți, SI corespunde celor mai mici 16 biți ESI și așa mai departe. Registrele de uz general, registrele de bază și registrele index pot fi utilizate ca bază în modurile de adresare, iar toate aceste registre, cu excepția indicatorului stivei, pot fi utilizate ca index în modurile de adresare.

Au fost adăugate două noi registre de segmente (FS și GS). Cu un număr mai mare de registre, instrucțiuni și operanzi, formatul codului mașinii a fost extins. Pentru a oferi compatibilitate inversă, segmentele cu cod executabil pot fi marcate ca conținând instrucțiuni de 16 sau 32 de biți. Prefixele speciale permit includerea instrucțiunilor pe 32 de biți într-un segment pe 16 biți sau invers .

80386 avea un coprocesor opțional în virgulă mobilă, 80387 ; avea opt registre largi de 80 de biți: st (0) până la st (7), ca 8087 și 80287. 80386 ar putea folosi și un coprocesor 80287. Cu 80486 și toate modelele x86 ulterioare, unitatea de procesare în virgulă mobilă (FPU) este integrată pe cip.

Pentium MMX adăugat opt 64-bit MMX întreg registre (MMX0 la MMX7, care împărtășesc biți mai mici cu stiva FPU 80-bit-lat). Cu Pentium III , Intel a adăugat un registru de control / stare (MXCSR) cu 32 de biți Streaming SIMD Extensions (SSE) și opt registre cu virgulă mobilă SSE pe 128 de biți (XMM0 până la XMM7).

Pe 64 de biți

Începând cu procesorul AMD Opteron , arhitectura x86 a extins registrele de 32 de biți în registre de 64 de biți într-un mod similar cu modul în care a avut loc extensia de 16 până la 32 de biți. Un prefix R (pentru „registru”) identifică registrele pe 64 de biți (RAX, RBX, RCX, RDX, RSI, RDI, RBP, RSP, RFLAGS, RIP) și opt registre generale suplimentare pe 64 de biți (R8-R15 ) au fost introduse și în crearea x86-64 . Cu toate acestea, aceste extensii sunt utilizabile numai în modul pe 64 de biți, care este unul dintre cele două moduri disponibile numai în modul lung . Modurile de adresare nu au fost schimbate dramatic din modul pe 32 de biți, cu excepția faptului că adresarea a fost extinsă la 64 de biți, adresele virtuale sunt acum semn extinse la 64 de biți (pentru a nu permite biții de mod în adresele virtuale), iar alte detalii ale selectorului au fost reduse dramatic . În plus, a fost adăugat un mod de adresare pentru a permite referințe de memorie relative la RIP ( indicatorul de instrucțiuni ), pentru a ușura implementarea codului independent de poziție , utilizat în bibliotecile partajate în unele sisteme de operare.

128 de biți

SIMD înregistrează XMM0 – XMM15.

256 de biți

SIMD înregistrează YMM0 – YMM15.

512 biți

SIMD înregistrează ZMM0 – ZMM31.

Diverse / scopuri speciale

Procesoarele x86 care au un mod protejat , adică procesoarele 80286 și ulterioare, au și trei registre descriptoare (GDTR, LDTR , IDTR ) și un registru de sarcini (TR).

Procesoarele x86 pe 32 de biți (începând cu 80386) includ, de asemenea, diverse registre speciale / diverse, cum ar fi registre de control (CR0 până la 4, CR8 numai pentru 64 de biți), registre de depanare (DR0 până la 3, plus 6 și 7), registre de testare (TR3 până la 7; numai 80486) și registre specifice modelului (MSR-uri, care apar cu Pentium).

AVX-512 are opt registre de mască suplimentare pe 64 de biți pentru selectarea elementelor dintr-un ZMM.

Scop

Deși registrele principale (cu excepția indicatorului de instrucțiuni) sunt „de uz general” în versiunile de 32 de biți și 64 de biți ale setului de instrucțiuni și pot fi utilizate pentru orice, inițial s-a prevăzut că acestea vor fi utilizate pentru următoarele scopuri:

- AL / AH / AX / EAX / RAX: acumulator

- BL / BH / BX / EBX / RBX: index de bază (pentru utilizare cu tablouri)

- CL / CH / CX / ECX / RCX: Contor (pentru utilizare cu bucle și corzi)

- DL / DH / DX / EDX / RDX: extindeți precizia acumulatorului (de exemplu, combinați EAX pe 32 de biți și EDX pentru operațiuni întregi pe 64 de biți în cod pe 32 de biți)

- SI / ESI / RSI: index sursă pentru operații de șir .

- DI / EDI / RDI: index de destinație pentru operații de șir.

- SP / ESP / RSP: indicator de stivă pentru adresa de sus a stivei.

- BP / EBP / RBP: Pointerul de bază al stivei pentru menținerea adresei cadrului curent al stivei .

- IP / EIP / RIP: indicator de instrucțiuni. Ține contorul programului , adresa următoarei instrucțiuni.

Registre de segmente:

- CS: Cod

- DS: Date

- SS: Stivă

- ES: Date suplimentare

- FS: Date suplimentare # 2

- GS: Date suplimentare # 3

Nu au fost prevăzute scopuri speciale pentru celelalte 8 registre disponibile numai în modul pe 64 de biți.

Unele instrucțiuni compilează și execută mai eficient atunci când se utilizează aceste registre în scopul proiectat. De exemplu, folosind AL ca un acumulator și adăugând o valoare imediată octet pentru a produce eficient Add to AL opcode de 04h, în timp ce folosind registrul BL produce generic și mai adăugați pentru a înregistra opcode de 80C3h. Un alt exemplu este împărțirea și multiplicarea cu precizie dublă care funcționează în mod specific cu registrele AX și DX.

Compilatoarele moderne au beneficiat de introducerea octetului sib (octet scale-index-base ) care permite ca registrele să fie tratate uniform (de tip minicomputer ). Cu toate acestea, utilizarea octetului sib universal nu este optimă, deoarece produce codificări mai lungi decât utilizarea acestuia selectiv numai atunci când este necesar. (Principalul beneficiu al octetului sib este ortogonalitatea și modurile de adresare mai puternice pe care le oferă, care fac posibilă salvarea instrucțiunilor și utilizarea registrelor pentru calculul adreselor, cum ar fi scalarea unui index.) Unele instrucțiuni speciale au pierdut prioritatea în proiectarea hardware-ului. și a devenit mai lent decât secvențele de cod mici echivalente. Un exemplu notabil este instrucțiunea LODSW.

Structura

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| R? X | |||||||

| E? X | |||||||

| ?X | |||||||

| ? H | ? L | ||||||

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| ? | |||||||

| ? D | |||||||

| W | |||||||

| ? B | |||||||

| 16 | 8 |

|---|---|

| ? S | |

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| R? P | |||||||

| E? P | |||||||

| ? P | |||||||

| ? PL | |||||||

Notă: Registrele? PL sunt disponibile numai în modul pe 64 de biți.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| R? Eu | |||||||

| Eu? | |||||||

| Eu | |||||||

| ? IL | |||||||

Notă: Registrele? IL sunt disponibile numai în modul pe 64 de biți.

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 |

|---|---|---|---|---|---|---|---|

| RIP | |||||||

| EIP | |||||||

| IP | |||||||

Moduri de operare

Mod real

Modul Adresă reală, denumit în mod obișnuit modul Real, este un mod de operare de procesoare compatibile cu 8086 și mai târziu x86 . Modul real este caracterizat de un spațiu de adresă de memorie segmentat pe 20 de biți (ceea ce înseamnă că poate fi adresat doar puțin mai mult de 1 MiB de memorie), acces direct al software-ului la hardware periferic și niciun concept de protecție a memoriei sau multitasking la nivel hardware. Toate procesoarele x86 din seria 80286 și ulterior pornesc în modul real la pornire; 80186 CPU și versiunile anterioare au avut un singur mod operațional, care este echivalent cu modul real în jetoanele ulterioare. (Pe platforma IBM PC, accesul direct al software-ului la rutinele IBM BIOS este disponibil numai în modul real, deoarece BIOS este scris pentru modul real. Cu toate acestea, aceasta nu este o proprietate a procesorului x86, ci a designului IBM BIOS.)

Pentru a utiliza mai mult de 64 KB de memorie, trebuie folosite registrele de segmente. Acest lucru a creat mari complicații pentru implementatorii de compilatoare care au introdus moduri de pointer ciudat, cum ar fi „aproape”, „departe” și „uriaș”, pentru a valorifica natura implicită a arhitecturii segmentate la diferite grade, cu unii indicatori care conțin compensări pe 16 biți în segmente implicite și altele pointeri care conțin adrese de segment și decalaje în segmente. Este posibil din punct de vedere tehnic să utilizați până la 256 KB de memorie pentru cod și date, cu până la 64 KB pentru cod, setând toate cele patru registre de segmente o singură dată și apoi numai folosind compensări pe 16 biți (opțional cu prefixe de suprascriere a segmentului implicit) la memoria de adrese, dar aceasta pune restricții substanțiale asupra modului în care datele pot fi adresate și operandii de memorie pot fi combinați și încalcă intenția arhitecturală a proiectanților Intel, care este ca elemente de date separate (de exemplu, tablouri, structuri, unități de cod) să fie conținute în segmente separate și adresate de propriile adrese de segmente, în programe noi care nu sunt portate de procesoare anterioare pe 8 biți cu spații de adrese pe 16 biți.

Modul ireal

Modul ireal este utilizat de unele sisteme de operare pe 16 biți și unele încărcătoare de încărcare pe 32 de biți .

Mod de gestionare a sistemului

Modul de gestionare a sistemului (SMM) este utilizat numai de firmware-ul sistemului ( BIOS / UEFI ), nu de sistemele de operare și software-ul aplicațiilor. Codul SMM rulează în SMRAM.

Mod protejat

Pe lângă modul real, Intel 80286 acceptă modul protejat, extinzând memoria fizică adresabilă la 16 MB și memoria virtuală adresabilă la 1 GB și oferind memorie protejată , care împiedică programele să se corupă reciproc. Acest lucru se face utilizând registrele de segmente numai pentru stocarea unui index într-un tabel descriptor care este stocat în memorie. Există două astfel de tabele, Tabelul descriptor global (GDT) și Tabelul descriptor local (LDT), fiecare conținând până la 8192 descriptori de segmente, fiecare segment oferind acces la 64 KB de memorie. În 80286, un descriptor de segment oferă o adresă de bază pe 24 de biți , iar această adresă de bază este adăugată la un offset de 16 biți pentru a crea o adresă absolută. Adresa de bază din tabel îndeplinește același rol pe care îl îndeplinește valoarea literală a registrului de segmente în modul real; registrele de segmente au fost convertite din registre directe în registre indirecte. Fiecărui segment i se poate atribui unul dintre cele patru niveluri de apel utilizate pentru securitatea computerelor bazate pe hardware . Fiecare descriptor de segment conține, de asemenea, un câmp de limită de segment care specifică decalajul maxim care poate fi utilizat cu segmentul. Deoarece compensările sunt de 16 biți, segmentele sunt încă limitate la 64 KB fiecare în modul protejat 80286.

De fiecare dată când un registru de segmente este încărcat în modul protejat, 80286 trebuie să citească un descriptor de segment de 6 octeți din memorie într-un set de registre interne ascunse. Astfel, încărcarea registrelor de segmente este mult mai lentă în modul protejat decât în modul real, iar schimbarea segmentelor foarte frecvent trebuie evitată. Operațiunile reale de memorie care utilizează segmente de mod protejat nu sunt încetinite prea mult, deoarece 80286 și ulterior au hardware pentru a verifica offsetul față de limita segmentului în paralel cu executarea instrucțiunilor.

Cele Intel 80386 offset extinse și , de asemenea , domeniul limită segment în fiecare descriptor de segment de 32 de biți, care să permită un segment de a cuprinde întregul spațiu de memorie. De asemenea, a introdus suport în modul protejat pentru paginare , un mecanism care face posibilă utilizarea memoriei virtuale paginate (cu dimensiunea paginii de 4 KB). Paginarea permite procesorului să mapeze orice pagină a spațiului de memorie virtuală la orice pagină a spațiului de memorie fizică. Pentru a face acest lucru, folosește tabele de mapare suplimentare în memorie numite tabele de pagini. Modul protejat pe 80386 poate funcționa cu paginarea activată sau dezactivată; mecanismul de segmentare este întotdeauna activ și generează adrese virtuale care sunt apoi mapate de mecanismul de paginare dacă este activat. Mecanismul de segmentare poate fi, de asemenea, dezactivat eficient prin setarea tuturor segmentelor pentru a avea o adresă de bază de 0 și o limită de dimensiune egală cu întregul spațiu de adrese; acest lucru necesită, de asemenea, un tabel descriptor de segment de dimensiuni minime, format din doar patru descriptori (deoarece segmentele FS și GS nu trebuie utilizate).

Paginarea este folosită pe scară largă de sistemele de operare moderne multitasking. Linux , 386BSD și Windows NT au fost dezvoltate pentru 386, deoarece a fost primul procesor de arhitectură Intel care a acceptat paging și offset-uri de segment pe 32 de biți. Arhitectura 386 a devenit baza tuturor dezvoltărilor ulterioare din seria x86.

Procesoarele x86 care acceptă modul protejat pornesc în modul real pentru compatibilitate inversă cu vechea clasă de procesoare 8086. La pornire (aka boot ), procesorul inițializează în modul real și apoi începe să execute instrucțiuni. Codul de pornire al sistemului de operare, care ar putea fi stocat în ROM , poate plasa procesorul în modul protejat pentru a activa paginarea și alte caracteristici. Instrucțiunile setate în modul protejat sunt similare cu cele utilizate în modul real. Cu toate acestea, anumite constrângeri care se aplică modului real (cum ar fi imposibilitatea de a utiliza ax, cx, dx în adresare) nu se aplică în modul protejat. În schimb, aritmetica segmentelor, o practică obișnuită în codul modului real, nu este permisă în modul protejat.

Mod 8086 virtual

Există, de asemenea, un sub-mod de funcționare în modul protejat pe 32 de biți (denumit și modul protejat 80386) numit modul virtual 8086 , cunoscut și sub numele de modul V86 . Acesta este în esență un mod special de operare hibrid care permite programelor în mod real și sistemelor de operare să ruleze în timp ce se află sub controlul unui sistem de operare supraveghetor în mod protejat. Acest lucru permite o mare flexibilitate în executarea simultană atât a programelor în mod protejat, cât și a programelor în mod real. Acest mod este disponibil exclusiv pentru versiunea pe 32 de biți a modului protejat; nu există în versiunea pe 16 biți a modului protejat sau în modul lung.

Mod lung

La mijlocul anilor 1990, era evident că spațiul de adrese pe 32 de biți al arhitecturii x86 își limita performanța în aplicații care necesită seturi mari de date. Un spațiu de adrese pe 32 de biți ar permite procesorului să adreseze direct doar 4 GB de date, o dimensiune depășită de aplicații precum procesarea video și motoarele de baze de date . Folosind adrese pe 64 de biți, este posibil să se adreseze direct 16 EiB de date, deși majoritatea arhitecturilor pe 64 de biți nu acceptă accesul la spațiul complet de adrese pe 64 de biți; de exemplu, AMD64 acceptă doar 48 de biți dintr-o adresă pe 64 de biți, împărțiți în patru niveluri de paginare.

În 1999, AMD a publicat o specificație (aproape) completă pentru o extensie pe 64 de biți a arhitecturii x86 pe care au numit-o x86-64 cu intențiile revendicate de a produce. Acest design este utilizat în prezent în aproape toate procesoarele x86, cu unele excepții destinate sistemelor încorporate .

Cipurile x86-64 produse în serie pentru piața generală au fost disponibile patru ani mai târziu, în 2003, după ce s-a petrecut timpul pentru ca prototipurile de lucru să fie testate și rafinate; cam în același timp, numele inițial x86-64 a fost schimbat în AMD64 . Succesul liniei de procesoare AMD64 împreună cu recepția călduță a arhitecturii IA-64 au forțat Intel să lanseze propria sa implementare a setului de instrucțiuni AMD64. Intel a implementat anterior suport pentru AMD64, dar a optat pentru a nu-l permite, sperând că AMD nu va aduce AMD64 pe piață înainte ca noul set de instrucțiuni IA-64 al Itanium să fie adoptat pe scară largă. Implementarea AMD64 a fost denumită EM64T și ulterior a fost redenumită Intel 64 .

În literatura de specialitate și numele versiunilor produselor, Microsoft și Sun se referă la AMD64 / Intel 64 în mod colectiv ca x64 în sistemele de operare Windows și Solaris . Distribuțiile Linux se referă la acesta fie ca "x86-64", varianta sa "x86_64", fie "amd64". Sistemele BSD folosesc „amd64” în timp ce macOS folosește „x86_64”.

Modul lung este în mare parte o extensie a setului de instrucțiuni pe 32 de biți, dar spre deosebire de tranziția de la 16 la 32 de biți, multe instrucțiuni au fost abandonate în modul pe 64 de biți. Acest lucru nu afectează compatibilitatea reală binară înapoi (care ar executa codul moștenit în alte moduri care păstrează suportul pentru acele instrucțiuni), dar schimbă modul în care trebuie să funcționeze ansamblorul și compilatoarele pentru codul nou.

Aceasta a fost prima dată când o extensie majoră a arhitecturii x86 a fost inițiată și originată de un alt producător decât Intel. A fost, de asemenea, prima dată când Intel a acceptat tehnologia de această natură dintr-o sursă externă.

Extensii

Unitate în virgulă mobilă

Procesoare x86 timpurie ar putea fi extins cu virgulă flotantă hardware sub forma unei serii de virgulă mobilă numeric co-procesoare cu nume precum 8087 , 80287 și 80387, X87 abreviat. Acest lucru a fost cunoscut și sub numele de NPX ( Numeric Processor eXtension ), un nume apt, deoarece coprocesoarele, deși utilizate în principal pentru calcule în virgulă mobilă, au efectuat, de asemenea, operații întregi atât pe formatele binare cât și pe cele zecimale. Cu foarte puține excepții, procesoarele 80486 și ulterioare x86 au integrat apoi această funcționalitate x87 pe cip, ceea ce a făcut din instrucțiunile x87 o parte integrantă de facto a setului de instrucțiuni x86.

Fiecare registru x87, cunoscut sub numele de ST (0) până la ST (7), are o lățime de 80 de biți și stochează numerele în formatul cu precizie extinsă dublă extinsă IEEE în virgulă mobilă . Aceste registre sunt organizate ca o stivă cu ST (0) ca vârf. Acest lucru a fost făcut pentru a conserva spațiul opcode și, prin urmare, registrele sunt accesibile aleatoriu numai pentru oricare operand dintr-o instrucțiune de înregistrare; ST0 trebuie să fie întotdeauna unul dintre cei doi operanzi, fie sursă, fie destinație, indiferent dacă celălalt operand este ST (x) sau un operand de memorie. Cu toate acestea, accesul aleator la registrele stivei poate fi obținut printr-o instrucțiune care schimbă orice ST (x) specificat cu ST (0).

Operațiile includ funcții aritmetice și transcendentale, inclusiv funcții trigonometrice și exponențiale, și instrucțiuni care încarcă constante comune (cum ar fi 0; 1; e, baza logaritmului natural; log2 (10); și log10 (2)) într-una dintre stiva se înregistrează. În timp ce abilitatea de număr întreg este adesea trecută cu vederea, x87 poate funcționa pe numere întregi mai mari, cu o singură instrucțiune decât 8086, 80286, 80386 sau orice procesor x86 fără extensii pe 64 de biți, și calcule întregi repetate chiar și pe valori mici (de exemplu, 16 biți) poate fi accelerat executând instrucțiuni întregi pe CPU x86 și x87 în paralel. (CPU x86 continuă să ruleze în timp ce coprocesorul x87 calculează, iar x87 setează un semnal la x86 când este terminat sau întrerupe x86 dacă are nevoie de atenție din cauza unei erori.)

MMX

MMX este un set de instrucțiuni SIMD proiectat de Intel și introdus în 1997 pentru microprocesorul Pentium MMX . Setul de instrucțiuni MMX a fost dezvoltat dintr-un concept similar folosit pentru prima dată pe Intel i860 . Este suportat de majoritatea procesoarelor IA-32 ulterioare de către Intel și alți furnizori. MMX este de obicei utilizat pentru procesarea video (de exemplu, în aplicații multimedia).

MMX a adăugat 8 registre noi la arhitectură, cunoscute sub denumirea de MM0 până la MM7 (denumită în continuare MMn ). În realitate, aceste noi registre nu erau decât aliasuri pentru registrele stive existente de x87 FPU. Prin urmare, orice s-a făcut stivei cu virgulă mobilă va afecta și registrele MMX. Spre deosebire de stiva FP, aceste registre MMn erau fixe, nu relative și, prin urmare, erau accesibile la întâmplare. Setul de instrucțiuni nu a adoptat semantica asemănătoare stivei, astfel încât sistemele de operare existente să poată salva și restabili în mod corect starea registrului atunci când fac multitasking fără modificări.

Fiecare dintre registrele MMn sunt numere întregi pe 64 de biți. Cu toate acestea, unul dintre conceptele principale ale setului de instrucțiuni MMX este conceptul de tipuri de date ambalate , ceea ce înseamnă că, în loc să folosiți întregul registru pentru un întreg întreg pe 64 de biți ( cuvânt quadruple ), îl puteți folosi pentru a conține două numere întregi de 32 de biți ( cuvânt dublu ), patru numere întregi de 16 biți ( cuvânt ) sau opt numere întregi de 8 biți ( octet ). Având în vedere că registrele MMN pe 64 de biți MMn sunt aliasate la stiva FPU și fiecare dintre registrele în virgulă mobilă are o lățime de 80 de biți, cei 16 biți superiori ai registrelor în virgulă mobilă sunt neutilizate în MMX. Acești biți sunt setați la toți prin orice instrucțiune MMX, care corespunde reprezentării în virgulă mobilă a NaN sau infinitelor.

3DNow!

În 1997, AMD a introdus 3DNow !. Introducerea acestei tehnologii a coincis cu creșterea aplicațiilor de divertisment 3D și a fost concepută pentru a îmbunătăți performanța procesării vectoriale a procesorului pentru aplicațiile cu intensitate grafică. Dezvoltatorii de jocuri video 3D și furnizorii de hardware de grafică 3D folosesc 3DNow! pentru a-și spori performanța pe seria de procesoare AM6 K6 și Athlon .

3DNow! a fost conceput pentru a fi evoluția naturală a MMX de la numere întregi la virgulă mobilă. Ca atare, folosește exact aceeași convenție de denumire a registrului ca MMX, adică MM0 până la MM7. Singura diferență este că, în loc să împacheteze numere întregi în aceste registre, două numere cu virgulă mobilă de o singură precizie sunt împachetate în fiecare registru. Avantajul aliasării registrelor FPU este că aceleași instrucțiuni și structuri de date utilizate pentru a salva starea registrelor FPU pot fi folosite și pentru a salva 3DNow! stări de înregistrare. Astfel, nu sunt necesare modificări speciale la sistemele de operare care altfel nu ar ști despre ele.

SSE și AVX

În 1999, Intel a introdus setul de instrucțiuni Streaming SIMD Extensions (SSE) , urmând în 2000 cu SSE2. Prima adăugare a permis descărcarea operațiilor de bază în virgulă mobilă din stiva x87 și a doua a făcut MMX aproape învechit și a permis ca instrucțiunile să fie direcționate în mod realist de către compilatoarele convenționale. Introdus în 2004 împreună cu revizuirea Prescott a procesorului Pentium 4 , SSE3 a adăugat memorie specifică și instrucțiuni de manipulare a firelor pentru a spori performanța tehnologiei Intel HyperThreading . AMD a licențiat setul de instrucțiuni SSE3 și a implementat majoritatea instrucțiunilor SSE3 pentru procesorul său de revizuire E și mai târziu Athlon 64. Athlon 64 nu acceptă HyperThreading și nu are acele instrucțiuni SSE3 utilizate numai pentru HyperThreading.

SSE a eliminat toate conexiunile vechi la stiva FPU. Acest lucru a însemnat, de asemenea, că acest set de instrucțiuni a eliminat toate conexiunile vechi la generațiile anterioare de seturi de instrucțiuni SIMD, cum ar fi MMX. Dar a eliberat proiectanții, permițându-le să utilizeze registre mai mari, nelimitate de dimensiunea registrelor FPU. Designerii au creat opt registre pe 128 de biți, denumite XMM0 până la XMM7. ( Notă : în AMD64 , numărul de registre SSE XMM a crescut de la 8 la 16.) Cu toate acestea, dezavantajul a fost că sistemele de operare trebuiau să cunoască acest nou set de instrucțiuni pentru a-și putea salva stările de înregistrare. . Așadar, Intel a creat o versiune ușor modificată a modului protejat, numită modul îmbunătățit, care permite utilizarea instrucțiunilor SSE, în timp ce acestea rămân dezactivate în modul normal protejat. Un sistem de operare care este conștient de SSE va activa modul îmbunătățit, în timp ce un sistem de operare necunoscut va intra doar în modul tradițional protejat.

SSE este un set de instrucțiuni SIMD care funcționează numai pe valori în virgulă mobilă, cum ar fi 3DNow !. Cu toate acestea, spre deosebire de 3DNow! elimină toate conexiunile vechi la stiva FPU. Deoarece are registre mai mari decât 3DNow !, SSE poate împacheta de două ori numărul de flotoare de precizie unice în registrele sale. SSE-ul original era limitat la numere cu o singură precizie, cum ar fi 3DNow !. SSE2 a introdus capacitatea de a împacheta și numere de precizie dublă , ceea ce 3DNow! nu a avut nicio posibilitate de a face, deoarece un număr de precizie dublă are dimensiunea de 64 de biți, care ar fi dimensiunea completă a unui singur 3DNow! MMn registru. La 128 de biți, registrele SSE XMMn ar putea împacheta două plutitoare de precizie dublă într-un singur registru. Astfel, SSE2 este mult mai potrivit pentru calculele științifice decât SSE1 sau 3DNow !, care erau limitate la o singură precizie. SSE3 nu introduce registre suplimentare.

Advanced Vector Extensions (AVX) a dublat dimensiunea registrelor SSE la registrele YMM pe 256 de biți. De asemenea, a introdus schema de codare VEX pentru a găzdui registre mai mari, plus câteva instrucțiuni pentru permutarea elementelor. AVX2 nu a introdus registre suplimentare, dar sa remarcat prin adăugarea instrucțiunilor de mascare, colectare și amestecare.

AVX-512 oferă încă o nouă extindere la 32 de registre ZMM de 512 biți și o nouă schemă EVEX. Spre deosebire de predecesorii săi cu o extensie monolitică, este împărțit în multe subseturi pe care modele specifice de procesoare le pot alege să le implementeze.

Extensie de adresă fizică (PAE)

Extensia de adresă fizică sau PAE a fost adăugată mai întâi în Intel Pentium Pro și mai târziu de AMD în procesoarele Athlon, pentru a permite adresarea a până la 64 GB RAM. Fără PAE, RAM-ul fizic în modul protejat pe 32 de biți este de obicei limitat la 4 GB . PAE definește o structură diferită a tabelului de pagini cu intrări mai largi în tabelul de pagini și un al treilea nivel de tabel de pagini, permițând biți suplimentari de adresă fizică. Deși implementările inițiale pe procesoare pe 32 de biți au acceptat teoretic până la 64 GB de memorie RAM, chipset-ul și alte limitări ale platformei au restricționat adesea ceea ce ar putea fi de fapt folosit. procesoarele x86-64 definesc structuri de tabele de pagini care teoretic permit până la 52 de biți de adresă fizică, deși, din nou, chipset-ul și alte probleme legate de platformă (cum ar fi numărul de sloturi DIMM disponibile și memoria RAM maximă posibilă pentru fiecare DIMM) împiedică o adresă fizică atât de mare spațiu de realizat. La procesoarele x86-64, modul PAE trebuie să fie activ înainte de trecerea la modul lung și trebuie să rămână activ în timp ce modul lung este activ, deci în modul lung nu există modul „non-PAE”. Modul PAE nu afectează lățimea adreselor liniare sau virtuale.

x86-64

În anii 2000, limitele procesorului x86 pe 32 de biți în adresarea memoriei erau un obstacol în calea utilizării lor în clustere de calcul de înaltă performanță și stații de lucru puternice pentru desktop. Vechiul 32-bit x86 concura cu arhitecturi RISC pe 64 de biți mult mai avansate, care ar putea aborda mult mai multă memorie. Intel și întregul ecosistem x86 aveau nevoie de adresarea memoriei pe 64 de biți pentru ca x86 să supraviețuiască erei de calcul pe 64 de biți, deoarece aplicațiile software pentru stații de lucru și desktop urmau să înceapă în curând să atingă limitele adresării pe memorie pe 32 de biți. Cu toate acestea, Intel a considerat că este momentul potrivit să facem un pas îndrăzneț și să folosim tranziția către computerele desktop pe 64 de biți pentru o tranziție departe de arhitectura x86 în general, un experiment care în cele din urmă a eșuat.

În 2001, Intel a încercat să introducă o arhitectură non-x86 pe 64 de biți denumită IA-64 în procesorul său Itanium , vizând inițial piața de calcul de înaltă performanță , sperând că va înlocui în cele din urmă x86 pe 32 de biți. În timp ce IA-64 a fost incompatibil cu x86, procesorul Itanium a oferit abilități de emulare pentru traducerea instrucțiunilor x86 în IA-64, dar acest lucru a afectat atât de grav performanța programelor x86 încât a fost rar, chiar dacă vreodată, de fapt util utilizatorilor: programatori ar trebui să rescrieți programele x86 pentru arhitectura IA-64 sau performanța lor pe Itanium ar fi ordine de mărime mai slabe decât pe un procesor x86 adevărat. Piața a respins procesorul Itanium, deoarece a întrerupt compatibilitatea înapoi și a preferat să continue să folosească cipuri x86 și foarte puține programe au fost rescrise pentru IA-64.

AMD a decis să ia o altă cale spre adresarea memoriei pe 64 de biți, asigurându-se că compatibilitatea inversă nu va avea de suferit. În aprilie 2003, AMD a lansat primul procesor x86 cu registre de uz general pe 64 de biți, Opteron , capabil să adreseze mult mai mult de 4 GB de memorie virtuală utilizând noua extensie x86-64 (cunoscută și sub numele de AMD64 sau x64). Extensiile pe 64 de biți ale arhitecturii x86 au fost activate numai în noul mod lung introdus , prin urmare aplicațiile și sistemele de operare pe 32 și 16 biți ar putea pur și simplu să continue să utilizeze un procesor AMD64 în moduri protejate sau în alte moduri, fără nici măcar cel mai mic sacrificiu al performanță și cu compatibilitate deplină înapoi la instrucțiunile originale ale Intel 8086 pe 16 biți. Piața a răspuns pozitiv, adoptând procesoarele AMD pe 64 de biți atât pentru aplicații de înaltă performanță, cât și pentru computerele de afaceri sau de acasă.

Văzând că piața respinge procesorul incompatibil Itanium și Microsoft care sprijină AMD64, Intel a trebuit să răspundă și a introdus propriul său procesor x86-64, Prescott Pentium 4, în iulie 2004. Ca urmare, procesorul Itanium cu setul său de instrucțiuni IA-64 este rar folosit și x86, prin întruparea sa x86-64, este încă arhitectura dominantă a procesorului în computerele neîncorporate.

x86-64 a introdus și bitul NX , care oferă o anumită protecție împotriva bug-urilor de securitate cauzate de depășirile de tampon .

Ca urmare a contribuției AMD pe 64 de biți la linia x86 și a acceptării sale ulterioare de către Intel, arhitecturile RISC pe 64 de biți au încetat să mai fie o amenințare pentru ecosistemul x86 și aproape că au dispărut de pe piața stațiilor de lucru. x86-64 a început să fie utilizat în supercomputerele puternice (în incarnările sale AMD Opteron și Intel Xeon ), o piață care anterior era habitatul natural pentru proiectele RISC pe 64 de biți (cum ar fi microprocesoarele IBM POWER sau procesoarele SPARC ). Saltul mare către calculul pe 64 de biți și menținerea compatibilității cu software-ul pe 32 de biți și pe 16 biți a permis arhitecturii x86 să devină astăzi o platformă extrem de flexibilă, cipurile x86 fiind utilizate de la sisteme mici de putere redusă (de exemplu, Intel Quark și Intel Atom ) către computere desktop de jocuri rapide (de exemplu, Intel Core i7 și AMD FX / Ryzen ) și chiar domină clustere mari de supercomputere , lăsând efectiv doar arhitectura ARM pe 32 și 64 de biți RISC ca concurent în piața smartphone - urilor și tabletelor .

Virtualizare

Înainte de 2005, procesoarele de arhitectură x86 nu puteau îndeplini cerințele Popek și Goldberg - o specificație pentru virtualizare creată în 1974 de Gerald J. Popek și Robert P. Goldberg . Cu toate acestea, atât produsele de hipervizor de virtualizare x86 proprietare, cât și cele open-source au fost dezvoltate utilizând virtualizarea bazată pe software . Sistemele proprietare includ Hyper-V , Parallels Workstation , VMware ESX , VMware Workstation , VMware Workstation Player și Windows Virtual PC , în timp ce sistemele gratuite și open-source includ QEMU , Kernel-based Virtual Machine , VirtualBox și Xen .

Introducerea seturilor de instrucțiuni AMD-V și Intel VT-x în 2005 a permis procesoarelor x86 să îndeplinească cerințele de virtualizare Popek și Goldberg.

AES

Vezi si

- limbaj de asamblare x86

- listări de instrucțiuni x86

- CPUID

- Itanium

- x86-64

- 680x0 , o arhitectură concurentă în epocile de 16 și 32 de biți

- PowerPC , o arhitectură concurentă în epocile ulterioare pe 32 și 64 de biți

- Microarhitectura

- Lista microprocesoarelor AMD

- Lista microprocesoarelor Intel

- Lista microarhitecturilor procesorului Intel

- Lista microprocesoarelor VIA

- Lista producătorilor x86

- Adresa de bază de intrare / ieșire

- Solicitare de întrerupere

- iAPX

- Modelul tick-toc

Note

Referințe

Lecturi suplimentare

- Rosenblum, Mendel; Garfinkel, Tal (mai 2005). „Monitoare de mașini virtuale: tehnologia actuală și tendințele viitoare”. Computer IEEE . 38 (5): 39–47. CiteSeerX 10.1.1.614.9870 . doi : 10.1109 / MC.2005.176 . S2CID 10385623 .

linkuri externe

- De ce Intel nu pare să retragă x86

- 32/64-bit x86 Instrucțiuni de referință

- Intel Intrinsics Guide , un instrument de referință interactiv pentru instrucțiunile intrinseci Intel

- Manualele dezvoltatorului de software pentru arhitecturi Intel® 64 și IA-32

- Ghiduri, manuale și documente ISA pentru dezvoltatori AMD, arhitectură AMD64